计算机组成原理

概论

发展史

- 电子管

- 晶体管

- 中小规模集成电路

- 大规模集成电路

性能指标

字长:一次能处理的二进制数据的位数

时钟频率:

运算速度:

- CPI(Clock cycle Per Instruction):执行一条指令所需要的时钟周期数。

- IPS(Instruction Per Second):每秒执行多少条指令,

- FLOPS:每秒执行多少次浮点运算。

内存容量:主存大小。

冯诺依曼结构

- 五大部分组成;

- 指令和数据以同等地位存储;

- 指令和数据用二进制表示;

- 指令由操作码和地址码组成;

- 存储程序;

- 以运算器为中心(早期)。

计算机构成

硬件系统:主机(CPU、控制器、主存)、外部设备或IO设备(硬盘、键盘、显示器等)

软件系统:系统软件、应用软件

计算机层次结构:

- M4:高级语言

- M3:汇编语言

- M2:操作系统机器(向上提供广义指令)

- M1:传统机器(执行机器语言指令)

- M0:微程序机器(执行微指令)

运算

定点数表示

| 表示 | 表示 | 8位表示范围 | |

|---|---|---|---|

| 原码 | |||

| 反码 | 正数:与原码一致 负数: |

||

| 补码 | 正数:与原码一致 负数: |

||

| 移码 | 补码符号位取反 | 只能表示整数 |

浮点数表示

科学计数法思想

- 阶码:补码或移码表示的定点整数,表示指数

- 尾数:原码或补码表示的定点小数,表示有效数字

规格化尾数:尾数的最高数值位必须是一个有效值。可以通过算数左移或算术右移来规格化尾数。

IEEE 754标准

| 类型 | 总位数 | 数符位数 | 阶码位数 | 尾数位数 |

|---|---|---|---|---|

| float | 32 | 1 | 8 | 23 |

| double | 64 | 1 | 11 | 52 |

| long double | 80 | 1 | 15 | 64 |

定点数的运算

移位

算数移位:左右移动位相当于乘除。

| 符号位移动 | 舍弃移出元素 | 空位填补内容 | |

|---|---|---|---|

| 算数移位 | × | √ | 原码: 反码:正数;负数 补码:正数;负数高位低位 |

| 逻辑移位 | √ | √ | |

| 循环移位 | √ | × | 移出的元素 |

加减

减法运算:减去一个值等于加上它的补数。

溢出判断:

正数 + 正数 = 负数,则上溢负数 + 负数 = 正数,则下溢

溢出检测:

- 单符号位:,时有溢出

- 单符号位和进位情况:、不同时有溢出

- 双符号位/变形补码:、时有溢出

乘法

原码乘法: 待补充

补码乘法: 待补充

除法

原码除法:待补充

补码除法:待补充

浮点数的运算

加减

- 对阶

- 尾数求和

- 规格化

- 左规

- 右规

- 舍入

- 0舍1入

- 恒置1

- 溢出判断

指令

指令格式

指令长度:一条指令所包含的二进制码的位数。有定长指令和变长指令两种结构。

操作码:有定长操作码和扩展操作码两种。

地址码:地址可以显式给出,也可以隐式给出。

| 类型指令 | 指令格式 | 操作方式 | 访存次数 | 下条指令 |

|---|---|---|---|---|

| 四地址指令 | 4 | |||

| 三地址指令 | 4 | |||

| 二地址指令 | 4 3 |

|||

| 一地址指令 | 3 2 |

|||

| 零地址指令 |

数据寻址

| 寻址方式 | 说明 |

|---|---|

| 隐含寻址 | 地址隐含在累加器中 |

| 立即寻址 | 和在一个字长内被同时取出 |

| 直接寻址 | →操作数 |

| 间接寻址 | →间接地址→操作数 |

| 寄存器直接寻址 | →寄存器中操作数 |

| 寄存器间接寻址 | →寄存器中间接地址→主存中操作数 |

| 变址寻址 | →变址,→形式地址,→操作数 |

| 基址寻址 | →基址,→形式地址,→操作数 |

| 相对寻址 | →操作数 |

| 堆栈寻址 |

指令系统

| CISC | RISC | |

|---|---|---|

| 代表架构 | x86 | ARM |

| 指令字长 | 不固定 | 定长 |

| 指令种类 | 多 | 少 |

| 访存指令 | 不加限制 | 仅LOAD/STORE |

| 通用寄存器数量 | 较少 | 多 |

| 指令流水线 | 可以实现 | 必须实现 |

| 各指令执行时间 | 相差较大 | 多数在一个周期内完成 |

| 各指令使用频度 | 相差很大 | 都比较常用 |

| 主要控制方式 | 微程序 | 组合逻辑 |

| 优化编译 | 无 | 有 |

存储器

存储器分类

按介质分类:半导体器件、磁性材料、光盘等

按存取方式:随机存储器、顺序存储器、半顺序存储器等

按作用分类:缓存、主存、闪存、辅存等

按读写功能:ROM、RAM等

- RAM:随机存储器,断电后信息丢失。

- SRAM:一般用作Cache。

- DRAM:有集中刷新、分散刷新、异步刷新三种。

- ROM:只读存储器。

- MROM:掩膜式ROM

- PROM:一次可编程ROM

- EPROM:可擦除可编程ROM

- Flash Memory:闪存

- 固态硬盘

| SRAM | DRAM | |

|---|---|---|

| 物理存储单元 | 触发器 | 电容 |

| 是否破坏性读出 | 否 | 是 |

| 是否需要刷新 | 否 | 是 |

| 行列地址传送 | 同时 | 分两次 |

| 运行速度 | 快 | 慢 |

| 集成度 | 低 | 高 |

| 发热量 | 大 | 小 |

| 存储成本 | 高 | 低 |

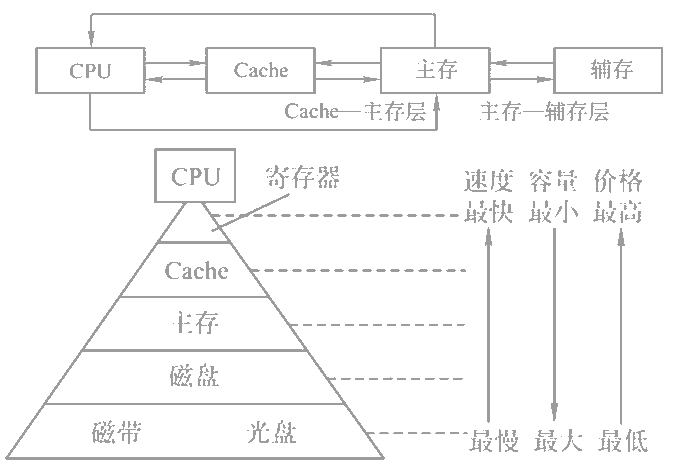

存储器层次结构

性能指标:

- 速度,

- 容量

- 单位价格

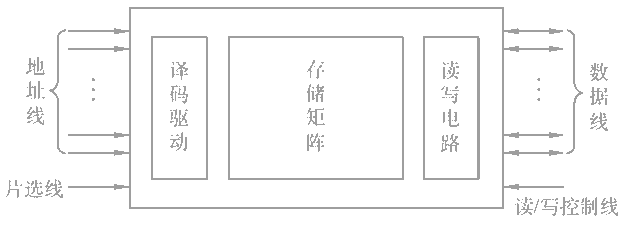

存储芯片基本结构:

- 地址总线():地址线数量应能覆盖所有存储单元。

- 数据总线():数据线数量应为位长。

- 控制总线

- 读控制线

- 写控制线

- 片选线

例:对于单个512K×8bit的芯片,有,。

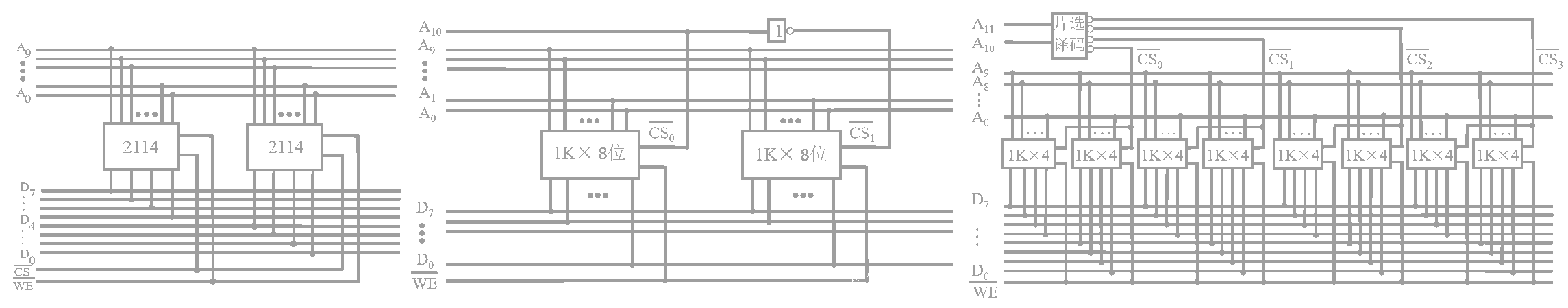

主存扩展

| 扩展 | 地址总线 | 数据总线 | |

|---|---|---|---|

| 位扩展 | 存储字长↑ | 每个芯片与全部地址总线相连 | 每个芯片仅与部分数据总线相连 |

| 字扩展 | 存储字容量↑ | 需要片选 | 每个芯片与全部数据总线相连 |

| 同时扩展 | 存储字长↑、存储字容量↑ |

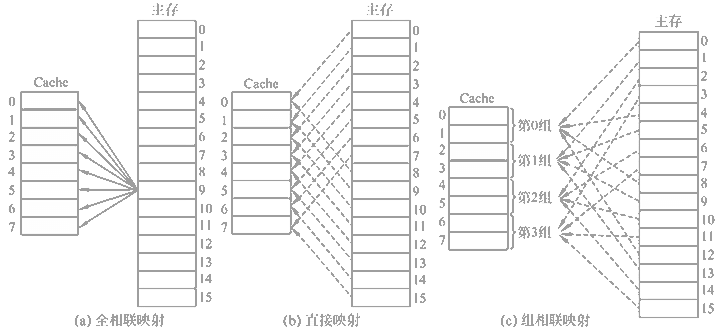

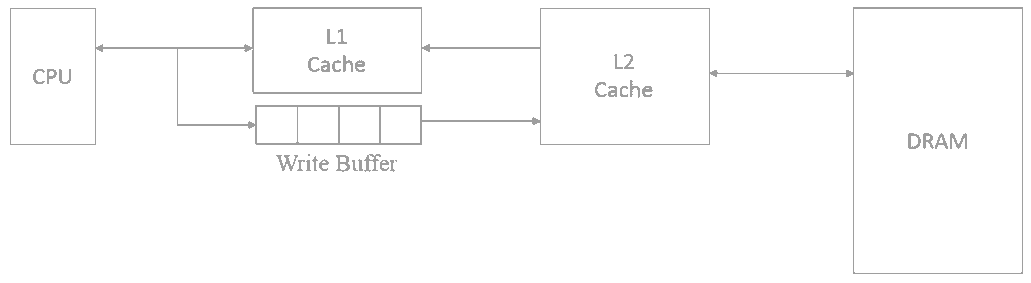

Cache策略

地址映射:

| 说明 | 优点 | 缺点 | |

|---|---|---|---|

| 全相联映射 | 字块可映射到Cache任何位置上 | 命中率高 | 所需逻辑电路多 |

| 直接映射 | 主存块仅能与Cache固定位置对应 | 实现简单 | 缓存利用率低 |

| 组相联映射 | 组采用直接映射,组内全相联映射 |

写策略:

- CPU与L1缓存:全写法+非写分配法

- L1缓存与L2缓存、L2缓存与主存:写回法+写分配法

替换算法:

- 随机算法

- 先进先出

- 近期最少使用(LRU)

- 最不经常使用(LFU)

处理器

CPU的功能

功能:指令控制、操作控制、时间控制、数据加工、中断处理。

运算器:算数运算、逻辑运算。

控制器:取指令、分析指令、执行指令、中断处理。

主要寄存器:通用寄存器、专用寄存器(指令寄存器IR、程序计数器PC、存储器数据寄存器MDR、存储器地址寄存器MAR、程序状态字寄存器PSWR)

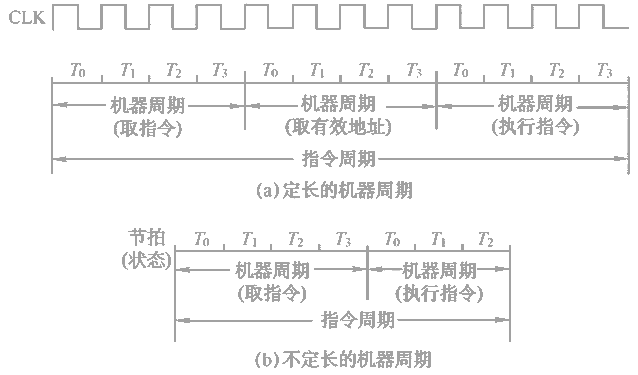

指令周期

指令周期:CPU从主存中每取出并执行一条指令所需的全部时间。

机器周期/CPU周期:指令周期常用若干机器周期来表示。

时钟周期/节拍:一个机器周期包含若干时钟周期,是CPU操作的最基本单位。

- 指令周期数据流:取指周期、间址周期、执行周期、中断周期。

- 指令执行方案:单指令周期、多指令周期、流水线方案。

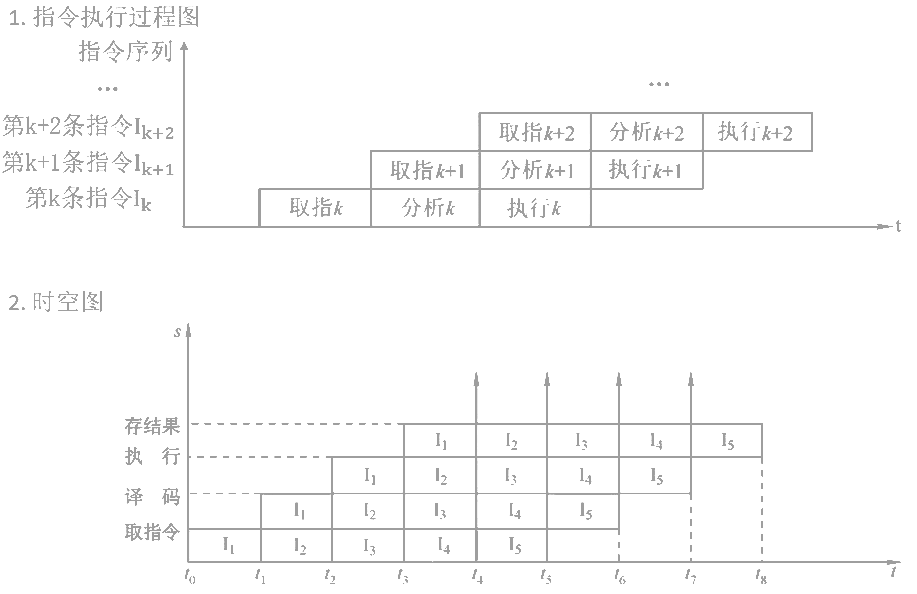

指令流水线

装入时间:第一个任务(例如)从开始到结束的时间。

排空时间:最后一个任务(例如)从开始到结束的时间。

性能指标

吞吐量(TP):单位时间内流水线所完成的任务数量,或是输出结果的数量。

- :一条指令执行分为个阶段。

- :任务数量。

- :一个时钟周期。

加速比:不使用流水线所用的时间与使用流水线所用的时间之比。

效率:个任务占用的时空区的有效面积。

影响流水线的因素

| 情况 | 说明 | 解决方案 |

|---|---|---|

| 结构/资源冲突 | 多指令在同一时刻争用同一资源 | 后一指令暂停一周期 资源重复配置 |

| 数据/数据冲突 | 后一条指令依赖前一条指令的执行结果 | 硬件阻塞(stall)、软件插入NOP 数据旁路技术 |

| 控制/控制冲突 | 转移等指令造成断流 | 尽早判别 预取双向目标指令 加快或提前形成条件码 提高分支预测成功率 |

流水线分类

- 根据使用级别:部件功能级、处理机级、处理机间

- 根据完成功能:单功能、多功能

- 根据同一时间各段连接方式:静态、动态

- 各功能段是否有反馈信号:线性、非线性

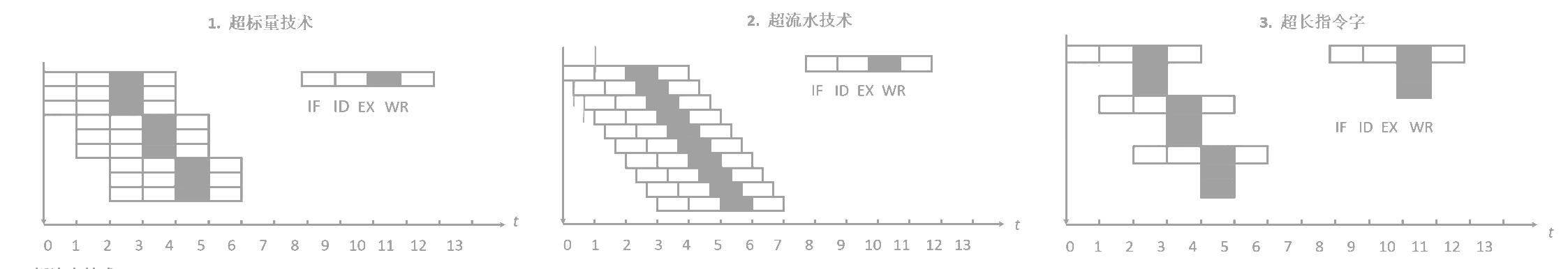

多发技术

- 超标量技术:每个时钟周期内并发多条指令,不能调整指令的执行顺序。

- 超流水技术:一个时钟周期内再分段,不能调整指令的执行顺序。

- 超长指令字

控制方式

- 同步控制方式

- 异步控制方式

- 联合控制方式

- 人工控制方式

微程序设计

即用程序设计的思想方法来组织操作控制逻辑。

微程序:一条机器指令对应一段微程序,微程序是一系列微指令的有序集合。

微指令:将操作控制信号按一定规则进行信息编码,存放在ROM中。

微命令:完成某个基本操作的命令,是最基本的不可被分解的命令。

微操作:与微命令一一对应,分为相容性和相斥性两种。

微指令编码:直接编码、字段编码(字段直接、字段间接)、最短编译法

微指令格式:水平型、垂直型

微地址的形成:增量方式、断定方式

总线

总线概念

总线特性:机械特性、电气特性、功能特性、时间特性

总线分类

按传输方式分为:串行、并行

按总线功能分为:片内、系统(数据、地址、控制)、通信

按时序分为:同步、异步

总线性能指标

总线传输周期:一次总线操作所需的时间,包括申请、寻址、传输、结束等阶段。

总线时钟周期:机器的时钟周期。

总线工作频率:总线传输周期的倒数。

总线时钟频率:总线时钟周期的倒数。

总线宽度:同时能传输的数据位数,通常指数据总线的根数。

总线带宽:数据传输率,单位时间总线上可传输数据的位数。

总线复用:一种信号线在不同时间传输不同的信息。

信号线数:地址总线、数据总线、控制总线等3种总线的总和。

总线标准

| 分类 | 串行 | 数据线 | 最大速度 | 补充 | |

|---|---|---|---|---|---|

| ISA | 系统总线 | × | 8, 16 | 16MB/s | 淘汰 |

| EISA | 系统总线 | × | 32 | 32MB/s | 淘汰 |

| PCI | 局部总线 | × | 32, 64 | 528MB/s | 即插即用 |

| AGP | 局部总线 | × | - | 2.1GB/s | 图形加速 |

| PCI-E | 局部总线 | √ | - | 10+GB/s | 点对点、全双工 |

| VESA | 局部总线 | 32 | 132MB/s | 高速视频传送 | |

| RS-232C | 设备总线 | √ | 9 | 20Kbps | 串口 |

| IDE/ATA | 设备总线 | × | 40 | 133MB/s | |

| SATA | 设备总线 | √ | 15+7 | 750MB/s | 串行ATA |

| SCSI | 设备总线 | × | - | 320MB/s | |

| SAS | 设备总线 | √ | - | 768MB/s | 串行SCSI |

| FireWire | 设备总线 | √ | - | 400MB/s | |

| USB | 设备总线 | √ | - | 热插拔 | |

| VGA | 视频总线 | 模拟信号 | |||

| DVI | 视频总线 | 模拟信号/数字信号 | |||

| DP | 视频总线 | 数字信号 | |||

| HDMI | 视频总线 | 数字信号 |

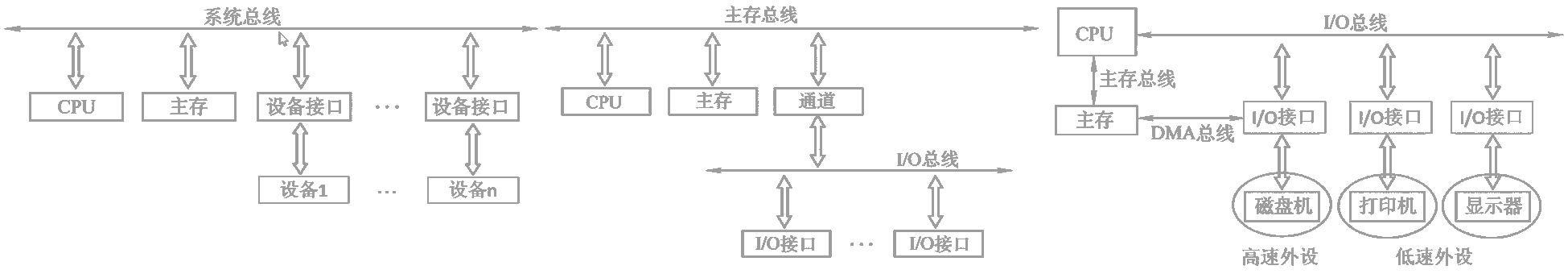

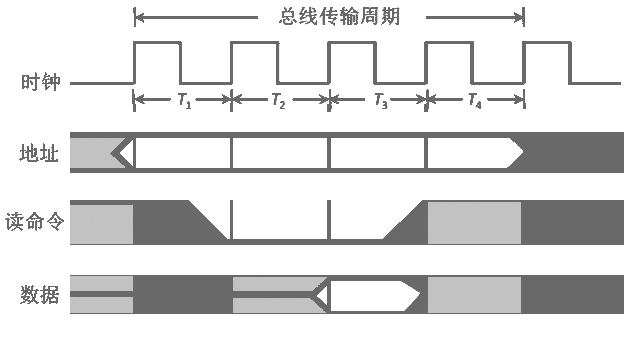

总线结构

- 单总线结构

- 双总线结构:低速I/O从单总线上分离

- 三总线结构:DMA用于高速I/O与主存直接交换信息

- 四总线结构:CPU总线、系统总线、高速总线、扩充总线

总线控制

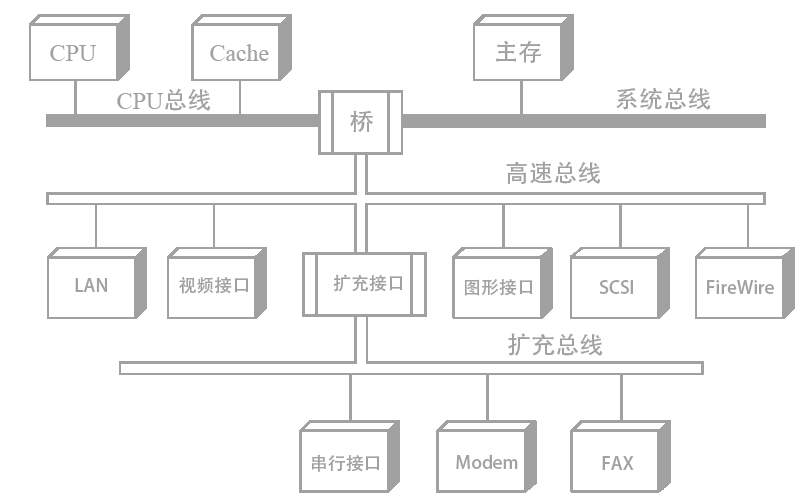

总线仲裁

主设备:获得总线控制权的设备。

从设备:被主设备访问的设备。

- BG:总线允许

- BR:总线请求

- BS:总线忙

| 控制线数 | 优点 | 缺点 | |

|---|---|---|---|

| 链式查询 | 总线请求: 总线允许: 总先忙: |

优先级固定; 结构简单; 容易扩充 |

对电路故障敏感; 优先级不灵活 |

| 计数器定时查询 | 总线请求: 总线允许: 总先忙: |

优先级灵活 | 控制线多; 控制相对复杂 |

| 独立请求 | 总线请求: 总线允许: 总先忙: |

响应速度快; 优先级灵活 |

控制线多; 控制复杂 |

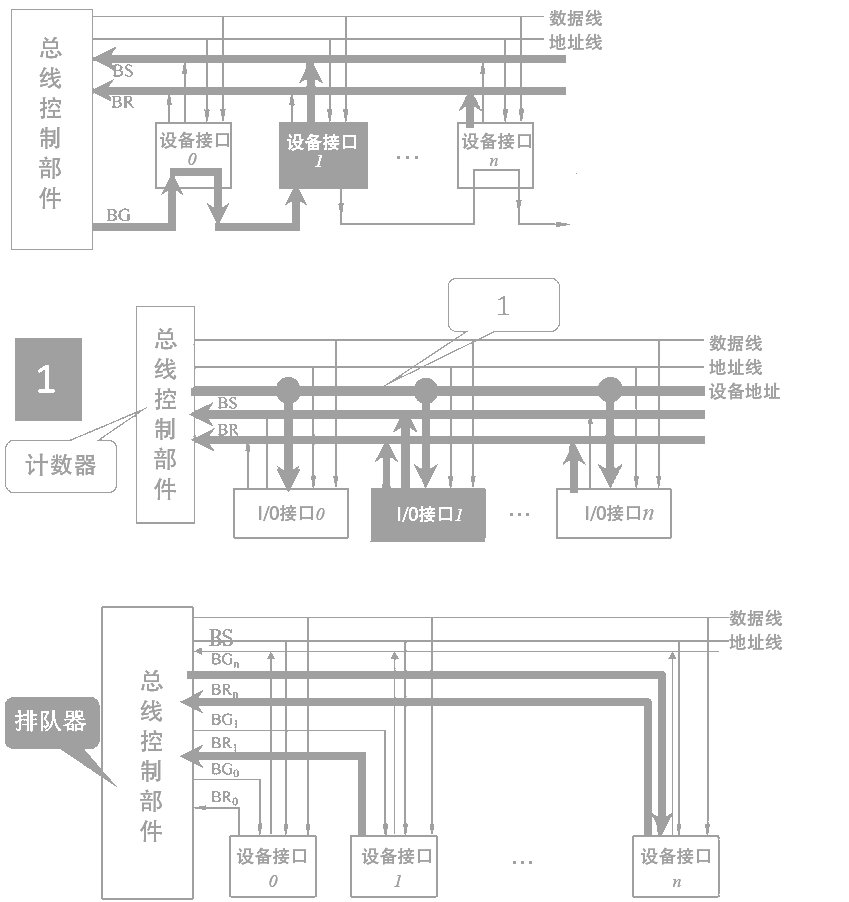

通信控制

| 说明 | |

|---|---|

| 同步定时 | 在一个总线周期中,发送方和接收方可进行一次数据传送 优点:速度快 缺点:主从强制同步 |

| 异步定时 | 分为不互锁、半互锁、全互锁三种 优点:总线周期长度可变 缺点:控制复杂、速度较慢 |

| 半同步通信 | 统一时钟的基础上,增加等待响应信号。 |

| 分离式通信 | 总线传输周期分为主模块占用和从模块占用 |

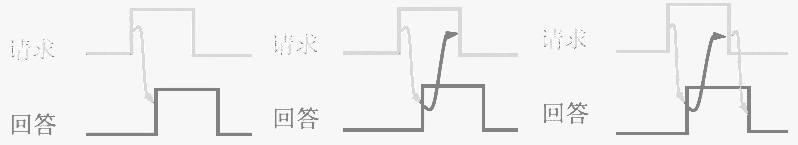

同步定时:

异步定时:

- 不互锁:主设备请求后不等待从设备回答信号,一段时间后便自动撤销请求信号。

- 半互锁:主设备请求后等待从设备回答信号;从设备不等待获知主设备请求信号已撤销,一段时间后便自动撤销回答信号。

- 全互锁:主设备请求后等待从设备回答信号;从设备回答后,等待主设备请求信号撤销再撤销回答信号。

外设

常见设备

磁盘

技术指标:记录密度、存储容量、平均寻址时间、数据传输率、误码率。

磁记录方式:归零制(RZ)、不归零制(NRZ)、“见1就翻”的不归零制(NRZ1)、调相制(PM)、调频制(FM)、改进型调频制(MFM)

显示器

性能指标:分辨率、灰度级、刷新率、点距、屏幕尺寸

打印机

分类:激光打印机、喷墨打印机

性能指标:打印速度、打印分辨率、最大打印尺寸

IO系统

IO接口功能:选址功能、传送命令功能、传送数据功能、反映IO设备工作状态功能

IO接口类型:

- 按传送方式:并行、串行

- 按灵活性:可编程、不可编程

- 按通用性:通用接口、专用接口

- 按传送方式:程序型接口、DMA型接口

主机与IO设备的联系:IO指令、编址方式、传送方式

主机与IO设备的传送控制:程序查询方式、程序中断方式、直接存储器存取DMA方式、IO通道控制方式

中断

中断提出方式:人为设置、程序性事故、硬件故障、IO设备、外部事件

中断处理过程:中断请求、中断判优、中断响应、中断服务(保护现场、中断服务、回复现场、中断返回)

中断屏蔽:单重中断、中断嵌套/多重中断(提前开中断、中断优先级)

DMA

DMA与CPU共享内存,DMA与内存交互方法有:

- CPU停止访问内存法:DMA向CPU发送停止信号

- DMA与CPU交替访问:时间片轮流访问

- 周期挪用法:挪用总线占用权几个内存周期